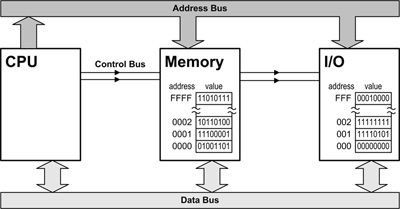

Consideriamo ora di nuovo l'architettura generale di un computer:

Supponiamo per semplicità che tutte le istruzioni del programma da eseguire siano già state caricate in memoria. Per fissare le idee, possiamo supporre che tali istruzioni occupino parole contigue in memoria, cioè ogni istruzione si trovi all'indirizzo dell'istruzione precedente più uno. Come si è già detto, le istruzioni non sono altro che sequenze di valori binari che la CPU (cioè il microprocessore) interpreta come altrettanti comandi da eseguire in sequenza.

La tabella seguente mostra come semplice esempio l'ipotetico contenuto delle prime tre parole di memoria (partendo dall'indirizzo zero):

| Indirizzo | Contenuto (codice operativo) | Istruzione |

| 00000000 | 0011 | istruzione1 |

| 00000001 | 1001 | istruzione2 |

| 00000010 | 1011 | istruzione3 |

Nell'esempio precedente la memoria ha 8 bit di indirizzo (e dunque 28=256 parole). Ogni parola di memoria è composta da 4 bit, usati per specificare il codice operativo di una singola istruzione del µP (i valori dei codici operativi sono stati scelti a caso). Il codice operativo è in pratica il codice numerico che rappresenta l'istruzione; ogni istruzione ha un proprio codice operativo e due istruzioni diverse non possono condividere lo stesso codice. Si noti che gli indirizzi sono sequenziali, cioè le istruzioni da eseguire sono memorizzate in sequenza.

In questo semplice esempio il bus indirizzi avrà dunque un'ampiezza di 8 bit e il bus dati avrà un'ampiezza di 4 bit (supponendo per semplicità, come si è detto, che ogni istruzione occupi una singola parola di memoria).

Ciclo di istruzione

Il ciclo di istruzione (Instruction Cycle, detto anche talvolta Ciclo di Fetch-Execute) è la sequenza di operazioni fondamentale eseguita ciclicamente dal microprocessore. Tale sequenza comporta il prelievo di un'istruzione dalla memoria, la sua decodifica e infine la sua esecuzione e viene ripetuta ciclicamente dal µP:

- il µP invia sul bus indirizzi l'indirizzo della successiva istruzione da eseguire;

- il µP invia alla memoria un comando di richiesta di accesso in memoria;

- il µP attende l'arrivo sul bus dati del codice operativo dell'istruzione prelevata dalla memoria;

- il µP decodifica l'istruzione;

- il µP esegue l'istruzione;

- l'esecuzione continua dal punto 1.

Le operazioni 1, 2 e 3 costituiscono la cosiddetta fase di prelievo (o fetch) dell'istruzione, la fase 4 è detta di decodifica e la fase 5 è detta di esecuzione (execute). La fase di fetch viene ripetuta allo stesso modo per tutte le istruzioni del programma, mentre ovviamentel e fasi di esecuzione e di decodifica variano da un'istruzione all'altra.

Esaminiamo ora più nel dettaglio le operazioni eseguite in un ciclo di istruzione. Esso si compone in generale di tre fasi eseguite in sequenza: fetch, decodifica, esecuzione.

Fase di fetch del codice operativo

La fase di fetch (o di prelievo) è la prima parte di un ciclo di istruzione e, come suggerisce il nome, effettua il prelievo di un'istruzione dalla memoria.

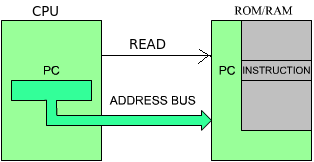

Si osservi la figura seguente:

L'indirizzo dell'istruzione (contenuto nel Program Counter, PC) viene inviato attraverso il bus indirizzi esterno alla memoria. Contemporaneamente il µP invia alla memoria un segnale di READ sul bus di controllo esterno, per indicare l'intenzione di leggere il contenuto di una parola di memoria.

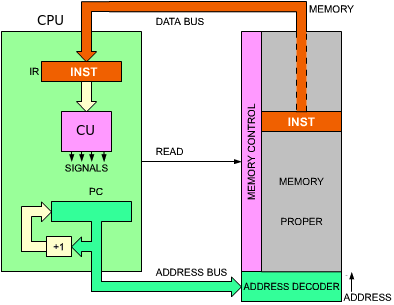

Dopo un tempo di ritardo (variabile da pochi ns a 1 µs), la memoria decodifica l'indirizzo ricevuto e deposita sul bus dati esterno il contenuto della locazione di memoria richiesta dal µP. A questo punto il µP può leggere il contenuto del bus dati e trasferirlo nell'IR (Instruction Register), il proprio registro interno dove viene memorizzato il codice operativo delle istruzioni da eseguire:

Si noti che, al termine della fase di fetch, il contenuto del Program Counter viene automaticamente incrementato di 1, in modo da puntare al successivo indirizzo in memoria.

Fase di decodifica e di esecuzione dell'istruzione

Dopo che il codice operativo è stato caricato nell'IR, l'unità di controllo (CU) interna al µP lo decodifica e quindi invia i segnali di controllo (SIGNALS in figura) agli altri componenti interni del µP in modo da eseguire l'istruzione stessa. Questa fase, detta di decodifica e di esecuzione, varia grandemente da un'istruzione all'altra (per esempio le operazioni da eseguire per effettuare una somma saranno del tutto diverse da quelle necessarie per spostare un blocco di dati da un'area all'altra della memoria).

A titolo di esempio consideriamo l'ipotetica istruzione R0 = R0+ R1, il cui significato è aggiungere al contenuto del registro R0 il contenuto del registro R1. A tale scopo per prima cosa il contenuto di R0 viene trasferito sul bus interno del µP fino all'accumulatore (che è collegato con uno dei due ingressi della ALU):

Quindi il contenuto del registro R1 viene trasferito sul bus interno fino al secondo ingresso della ALU. Tale ingresso corrisponde a un buffer o registro temporaneo (TMP in figura) dove il valore viene memorizzato temporaneamente:

Infine la ALU effettua la somma e il risultato viene trasferito sul bus interno fino al registro R0:

Si noti che l'operazione effettuata modifica anche il contenuto del registro dei flag (che segnalano, come si è detto, se il risultato è positivo, negativo, uguale a zero, etc.).

Tutte le operazioni effettuate nella fase di execute vengono coordinate dalla Control Unit, la quale abilita a turno i diversi registri del µP in modo che possano, a seconda dei casi, leggere oppure scrivere (solo uno alla volta) sul bus dati interno.

Il numero di istruzioni (cioè di codici differenti) che il µP può eseguire è legato alla dimensione della parola (word) della memoria esterna, cioè all'ampiezza del bus dati del µP. Supponendo che ogni istruzione occupi una sola parola da n bit, il numero di istruzioni totali sarà dunque semplicemente 2n. In realtà praticamente tutti i µP prevedono la possibilità di istruzioni formate da più parole, estendendo in tal modo il massimo numero di istruzioni eseguibili.

Oltre al codice operativo, molte istruzioni contengono anche uno o più operandi (cioè valori su cui l'istruzione deve operare). Per esempio un'istruzione potrebbe essere così composta:

| Indirizzo in memoria | Contenuto | Significato |

| 00000011 | 0011 | Carica nel registro A (codice operativo) |

| 00000100 | 0000 | il valore 0000 (operando) |

Nel caso di istruzioni con più operandi, il codice operativo è costituito sempre dalla prima (o dalle prime) parole, mentre gli operandi occupano le parole successive in memoria.

Se l'istruzione contiene operandi la fase di esecuzione dell'istruzione implica ulteriori prelievi (fetch) in memoria per ottenere gli operandi dell'istruzione stessa. In generale le operazioni di fetch degli operandi sono molto simili al fetch del codice operativo dell'istruzione e vengono effettuate nello stesso modo.

Sito realizzato in base al template offerto da

http://www.graphixmania.it