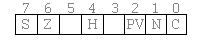

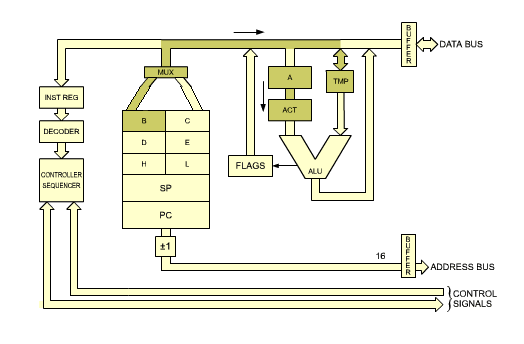

La figura seguente mostra l'architettura interna dello Z80:

Esaminiamone più nel dettaglio le parti fondamentali:

- i tre bus interni (data bus a 8 bit, address bus a 16 bit e control bus) si interfacciano all'esterno del µP con i corrispondenti tre bus esterni;

- la parte indicata con Control Section rappresenta la logica di decodifica e controllo dello Z80 (precedentemente indicata come Control Unit);

- i registri A, B, C, D, E, F, H, I, L e R sono a 8 bit, mentre IX, IY, SP e PC sono registri a 16 bit;

- i registi A', B', C', D', E', F', H' e L' sono copie dei corrispondenti registri "principali" A, B etc. il cui contenuto può essere rapidamente scambiato con quello dei registri principali attraverso un'istruzione di exchange (EXX, serve per salvare e ripristinare rapidamente lo stato del µP).

- il registro A è l'accumulatore, cioè il registro usato in tutte le operazioni effettuate dalla ALU;

- il registro è F, detto Flag Register, memorizza nei suoi bit lo stato dell'ultima operazione compiuta dalla ALU; il contenuto del registro F nel dettaglio è mostrato qui sotto:

dove C indica se c'è un riporto dall'ultima operazione eseguita), P/V nelle operazioni matematiche indica l'eventuale overflow mentre nelle operazioni logiche indica la parità pari o dispari del risultato, Z indica se il risultato dell'ultima operazione è zero, S indica il segno positivo o negativo del risultato (i bit 1, 3, 4 e 5 del registro F sono usati per operazioni interne del µP oppure non sono utilizzati); - i registri B, C, D, E, H e L sono registri general purpose, cioè sono di uso generico e vengono usati in tutte le principali istruzioni dello Z80;

- i registri BC, DE e HL possono anche essere utilizzati a coppie, come se si trattasse di un unico registro a 16 bit;

- i registri di indice IX e IY sono a 16 bit e vengono usati per memorizzare indirizzi in memoria; questi registri sono collegati con un addizionatore (indicato sullo schema col simbolo di una piccola ALU) che permette di sommare al loro contenuto un valore proveniente dal bus dati (detto displacement);

- PC è il Program Counter, ovvero il registro/contatore incrementato automaticamente che punta sempre all'indirizzo di memoria della prossima istruzione da eseguire.

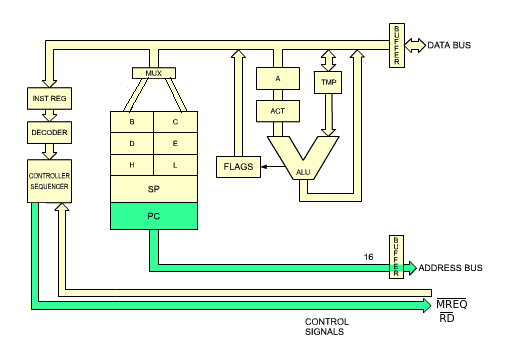

Fetch di un'istruzione

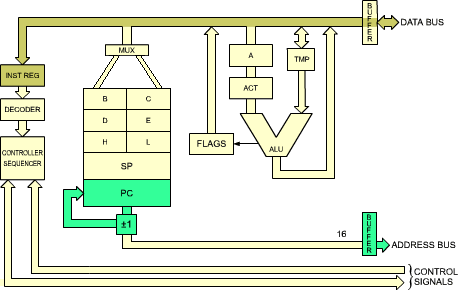

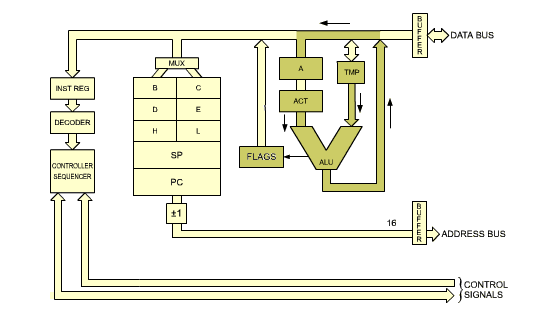

Con riferimento all'architettura interna dello Z80, esaminiamo adesso nel dettaglio le operazioni interne compiute dal µP per prelevare (fetch) il codice operativo di un'istruzione dalla memoria.

Per prima cosa l'indirizzo dell'istruzione dev'essere messo sul bus indirizzi esterno. Siccome l'indirizzo della prossima istruzione da eseguire è contenuto nel Program Counter (PC), il µP invia il contenuto del PC sul bus indirizzi esterno. Contemporaneamente vengono inviati alla memoria anche i segnali di controllo per l'operazione di lettura (RD e MREQ):

Mentre la memoria viene letta, il PC viene automaticamente incrementato (PC=PC+1) in modo da essere già pronto con l'indirizzo della successiva istruzione da eseguire.

Quindi il codice operativo dell'istruzione (fornito dalla memoria) viene trasferito dal bus dati esterno all'Instruction Register, per poter essere eseguito e decodificato:

Decodifica ed esecuzione di un'istruzione

Mentre la fase di fetch del codice operativo è comune a tutte le istruzioni, la fase di decodifica ed esecuzione dipende invece dalla particolare istruzione che deve essere eseguita.

Consideriamo a titolo di esempio l'esecuzione dell'istruzione

ADD A,B

la quale somma il contenuto del registro A con il contenuto del registro B e mette il risultato nuovamente in A.

Per prima cosa l'unità di controllo decodifica il codice operativo dell'istruzione e quindi abilita il trasferimento sul bus dati interno del contenuto del registro B fino al registro temporaneo collegato con uno dei due ingressi della ALU:

Infine la ALU effettua la somma fra l'accumulatore e il registro temporaneo e il risultato viene nuovamente caricato nell'accumulatore attraverso il bus dati interno. Si noti che il contenuto del Flag Register viene modificato in base al risultato dell'operazione (positivo, negativo, nullo, con o senza riporto, etc.):

Fetch/execute overlap

Una caratteristica interessante dell'architettura dello Z80 è il cosiddetto fetch/execute overlap (ovvero sovrapposizione di prelievo ed esecuzione). In pratica, per aumentare la velocità, durante la fase di esecuzione di un'istruzione che non richiede l'accesso ai bus esterni (per esempio un'addizione fra due registri interni al µP) lo Z80 accede alla memoria per prelevare l'istruzione successiva da eseguire.

Un diagramma temporale esemplificativo è mostrato in figura:

Naturalmente non per tutte le istruzioni è possibile questo pre-caricamento dell'istruzione successiva. In particolare l'overlap è impossibile per le istruzioni che devono accedere alla memoria esterna durante la fase di esecuzione. E' compito dell'Unità di Controllo interna al µP determinare in ogni caso se una data istruzione consente oppure no il fetch contemporaneo dell'istruzione successiva.

Sito realizzato in base al template offerto da

http://www.graphixmania.it