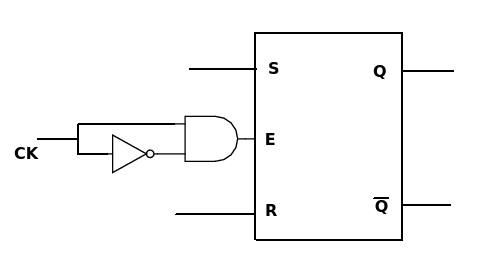

In modo analogo a quanto visto col flip flop D, è possibile trasformare un latch SR (non sincronizzato, con segnale di abilitazione) in flip flop SR sincronizzato (attivo sul fronte del clock). Lo schema di riferimento è il seguente:

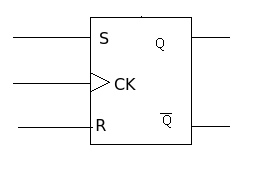

Il simbolo circuitale e la tabella di verità sono le seguenti:

|

|

Ovviamente è possibile costruire in modo molto simile un flip flop set reset pilotato sul fronte di discesa del clock.

Flip flop JK

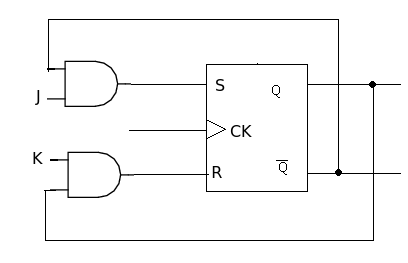

Si consideri ora il seguente schema circuitale:

Ricordandoci che le porte AND forniscono un livello H in uscita solo quando entrambi gli ingressi sono H (ovvero che basta che almeno uno degli ingressi sia L perché anche l'uscita sia L), studiamo il funzionamento del circuito nei quattro casi possibili.

- Se J=0 e K=0 → S = 0 e R = 0 → Q = Q0 e Q = Q0

Il flip flop memorizza lo stato precedente.

- Se J=0 e K=1, sicuramente si avrà S=0.

Per quanto riguarda invece R, occorre conoscere il valore presente su Q. Infatti se Q = 0 allora R = 0; se invece Q = 1, si avrà R = 1. In entrambi i casi il flip flop si porta in uno stato di reset, cioè con Q = 0 e Q = 1. - In modo perfettamente simile al precedente, se J=1 e K=0 il flip flop viene settato, cioè si porta in uno stato con Q = 1 e Q = 0. In pratica gli ingressi J e K agiscono come i corrispondenti ingressi S e R.

- Se J=1 e K=1 abbiamo due possibilità:

a) se Q = 0 e Q = 1 → S = 1 e R = 0 → Q = 1 e Q = 0

b) se Q = 1 e Q = 0 → S = 0 e R = 1 → Q = 0 e Q = 1

In pratica con J=1 e K=1 le uscite commutano sempre (toggle in inglese), ovvero cambiano valore in ogni caso.

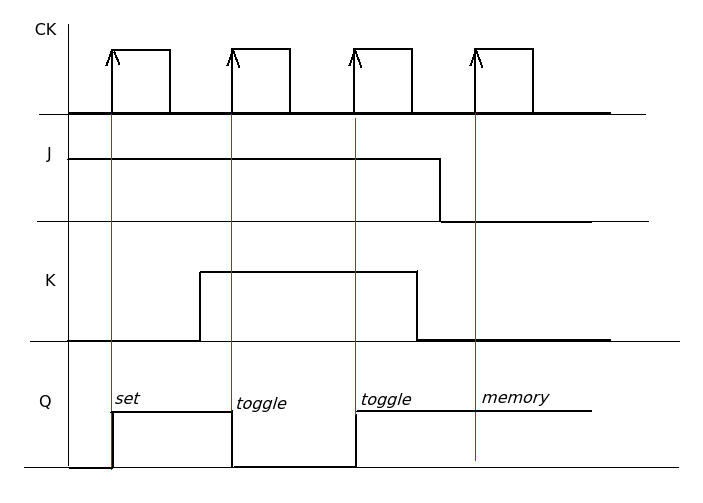

Si osservi che con questa configurazione la "combinazione proibita" S=1 e R=1 non si presenta mai in ingresso al flip flop. Il seguente cronogramma dovrebbe chiarire il funzionamento del componente:

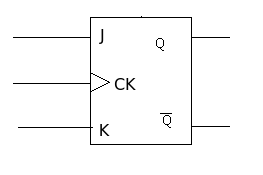

Il simbolo circuitale e la tabella di verità del flip flop JK sono mostrati qui sotto:

Il simbolo circuitale e la tabella di verità del flip flop JK sono mostrati qui sotto:

|

|

Come si può notare la tabella di verità del ff KK è quasi identica a quella del ff SR, tranne per l'ultimo caso. In pratica il ff JK è un ff SR in cui la configurazione proibita viene trasformata in una configurazione che provoca la commutazione dell'uscita.

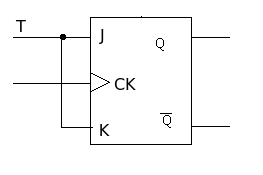

Flip flop T (toggle)

Il flip flop T (toggle) può essere facilmente ottenuto dal ff JK collegando insieme i due ingressi:

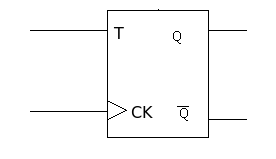

Simbolo elettrico e tabella di verità del flip flop T sono mostrati in figura:

|

|

Questo flip flop presenta solo due modi di funzionamento:

- se T=0 il flip flop memorizza lo stato precedente;

- se T=1 lo stato del flip flip commuta cambiando valore (toggle).

Il flip flop T non è disponibile come circuito integrato, dato che può essere realizzato con estrema facilità collegando insieme i due ingressi di un flip flop JK.

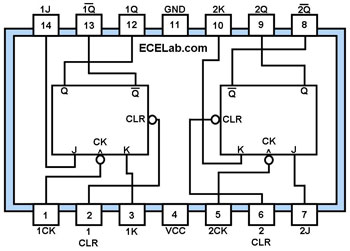

Flip flop integrati

Il flip flop set-reset e il flip flop T non sono disponibili come circuiti integrati, mentre si trovano diverse versioni del flip flop JK per tutte le principali famiglie logiche. A titolo di esempio mostriamo la piedinatura del 7473, un integrato TTL contenente due ff JK pilotati sul fronte di discesa del clock (si noti l'ingresso asincrono di clear):

Sito realizzato in base al template offerto da

http://www.graphixmania.it