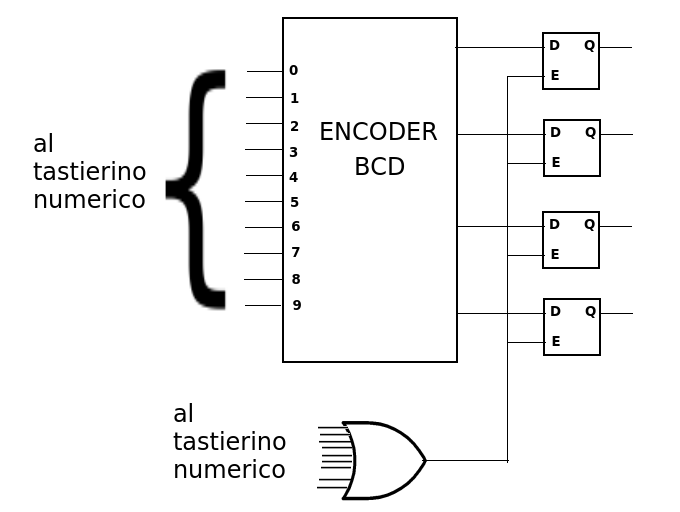

Esaminiamo nuovamente il circuito che utilizza latch D per memorizzare i codici prodotti da un tastierino numerico:

Notiamo che il circuito presenta un potenziale problema di funzionamento. Infatti l'abilitazione (ingresso E) dei latch D viene fornita dalla pressione di un tasto attraverso la porta OR. Quando il tasto viene rilasciato, l'abilitazione viene tolta e il dato dovrebbe rimanere memorizzato nei latch.

Notiamo che il circuito presenta un potenziale problema di funzionamento. Infatti l'abilitazione (ingresso E) dei latch D viene fornita dalla pressione di un tasto attraverso la porta OR. Quando il tasto viene rilasciato, l'abilitazione viene tolta e il dato dovrebbe rimanere memorizzato nei latch.

Il problema è che, contemporaneamente, quando viene rilasciato il tasto, cambia anche l'ingresso dell'encoder e dunque cambia anche il valore presente sugli ingressi D dei latch. Se il valore fornito dall'encoder si modifica prima che venga tolta l'abilitazione, il dato memorizzato non è più valido!

Ritardo di propagazione

Si dice ritardo di propagazione (propagation delay) di un circuito logico il tempo che passa fra la commutazione di un ingresso e la corrispondente commutazione dell'uscita. La figura seguente mostra il ritardo di propagazione in una porta NOT:

In teoria il ritardo di propagazione dovrebbe essere zero, ma ovviamente così non è, anche se per una singola porta logica i valori sono piuttosto piccoli. La tabella seguente mostra i valori del ritardo di propagazione per le porte di diverse famiglie logiche (si noti che si tratta di valori sempre nell'ordine di alcuni nanosecondi):

Famiglia |

Ritardo (ns) |

| CMOS 4000 | 300 |

| HCMOS | 23 |

| CMOS ACL | 9,5 |

| TTL LS | 15 |

| TTL FAST | 6 |

Chiaramente quando in un circuito logico vengono collegate più porte in cascata (con l'uscita dell'una collegata con l'ingresso della successiva) il ritardo di propagazione aumenta.

Tornando quindi al nostro encoder collegato col tastierino numerico, il circuito presenta un potenziale problema di sincronizzazione che dipende dai ritardi di propagazione della porta OR e dell'encoder. Infatti, quando il tasto viene rilasciato, se il ritardo dell'OR è minore di quello dell'encoder, l'enable viene disattivato prima che "scompaia" il dato da memorizzare e la memorizzazione avviene dunque correttamente; viceversa se l'encoder fosse più veloce dell'OR, il dato memorizzato sui latch potrebbe non essere corretto.

Dato che l'encoder è internamente realizzato con un circuito logico comprendente più porte, è probabile che esso sia più lento della porta OR e che dunque la memorizzazione in questo esempio avvenga correttamente. E' tuttavia chiaro che in circuiti più complicati non è possibile fare affidamento sui differenti tempi di propagazione dei sotto-circuiti logici affinché il funzionamento sia corretto. Occorre una soluzione migliore per sincronizzare con maggiore precisione la memorizzazione dei dati.

Sito realizzato in base al template offerto da

http://www.graphixmania.it