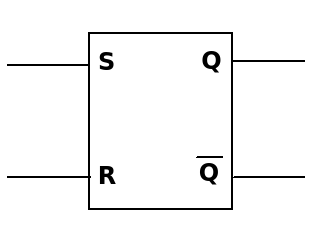

Il circuito con due porte NOR studiato nella lezione precedente si chiama latch set-reset (o più brevemente latch SR) e viene rappresentato col seguente simbolo:

Il termine inglese latch significa "serratura a scatto" e descrive abbastanza bene il comportamento del componente. L'ingresso S viene detto ingresso set, mentre R è l'ingresso reset. Le uscite si chiamano Q e Q perché sono l'opposta l'una dell'altra (tranne in un caso particolare che dobbiamo ancora esaminare: quando S=1 e R=1).

L'ingresso set serve per settare, cioè per mandare a livello alto l'uscita Q (e conseguentemente a livello basso l'uscita Q). Analogamente l'ingresso R serve per resettare, cioè per mandare a livello basso l'uscita Q (e livello alto l'uscita Q).

Quando entrambi gli ingressi sono a livello basso (S=0 e R=0) le uscite conservano lo stato precedente, ovvero mantengono i valori che avevano prima. In un certo senso il latch SR è un dispositivo di memoria elementare, in grado di memorizzare un singolo bit di informazione (si tratta di un solo bit, anche se le uscite sono due, perché i valori delle due uscite non sono indipendenti, ma l'una è l'opposto dell'altra).

Questo particolare funzionamento viene indicato nella tabella di verità in modi diversi, come mostrato qui sotto:

|

|

|

La combinazione di ingressi S=1 e R=1

La combinazione in cui entrambi gli ingressi sono a livello alto (S=1 e R=1) non viene nella pratica mai usata in quanto produce una configurazione "non valida" delle uscite (in cui entrambe le uscite, Q e Q, valgono 0). E' facile d'altra parte accorgersi che la presenza contemporanea di un ingresso set e di un ingresso reset è contraddittoria: cosa vuol dire infatti settare e resettare contemporaneamente le uscite? Sarebbe un po' come voler spegnere e accendere nello stesso tempo un dispositivo

Inoltre la combinazione S=1 e R=1 produce risultati ambigui poiché se si passa da S=1 a R=1 alla combinazione S=0 e R=0, il valore presente in uscita dipende da quello dei due ingressi che si azzera per ultimo (dal momento che l'azzeramento perfettamente contemporaneo di due segnali elettrici è fisicamente impossibile).

Per tutte queste ragioni, il progettista che usa latch SR deve prestare sempre particolare attenzione al fatto che la combinazione S=1 e R=1 non venga mai a verificarsi nel proprio circuito.

Questo fatto viene spesso indicato così sulla tabella di verità del latch:

| S | R | Q | Q |

|---|---|---|---|

| 0 | 0 | Q0 | Q0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | not used | not used |

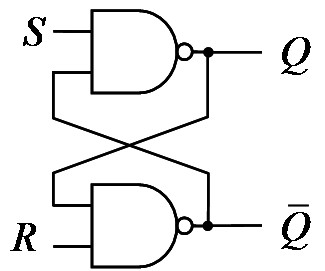

Il latch set-reset a porte NAND

Esiste una realizzazione circuitale alternativa per il latch SR che fa uso di porte NAND:

La tabellla di verità è la seguente:

| S | R | Q | Q |

|---|---|---|---|

| 0 | 0 | not used | not used |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Q0 | Q0 |

Questo tipo di circuito funziona in logica invertita ovvero in logica negativa: per attivare un ingresso (per esempio S) bisogna fornire un valore basso (cioè 0 nella nostra tabella); per disattivarlo bisogna invece fornire un valore alto.

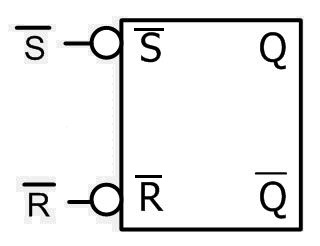

Questo fatto viene indicato nel seguente modo nel simbolo circuitale del latch:

Si osservi il simbolo di negazione e il "pallino" sugli ingressi che funzionano in logica negativa.

Il latch set-reset integrato

Il latch SR è disponibile anche come integrato della serie CMOS e TTL. A titolo di esempio la figura seguente mostra un 74118 contenente 6 latch SR a porte NAND. Si noti che, per risparmiare sul numero di piedini, l'ingresso di reset è unico per tutti i latch sull'integrato:

Circuiti logici sequenziali

Il latch SR è il primo e più semplice circuito appartenente alla categoria dei cosiddetti circuiti logici sequenziali. Come già sappiamo, nei circuiti combinatori (porte logiche, encoder, multiplexer etc) l'uscita dipende solo dal valore degli ingressi nel medesimo istante di tempo.

Nei circuiti sequenziali invece l'uscita può dipendere anche dallo stato precedente del circuito. Nel caso del latch SR questa dipendenza è evidente nel caso in cui entrambi gli ingressi sono a livello basso (S=0 e R=0). In tale condizione per conoscere i valori delle uscite non basta conoscere i valori degli ingressi: occorre conoscere anche lo stato precedente delle uscite stesse.

Come abbiamo già accennato e come sarà maggiormente chiarito nel seguito, i circuiti sequenziali sono circuiti con "memoria", in quanto il loro stato dipende dagli stati passati del circuito stesso.

Sito realizzato in base al template offerto da

http://www.graphixmania.it