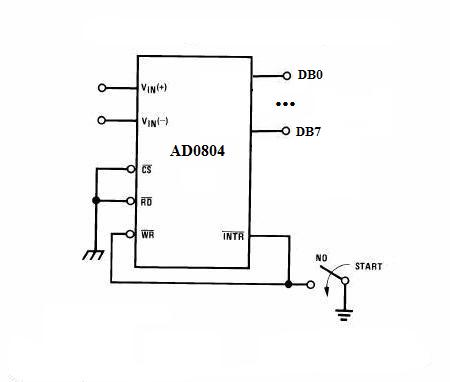

Il modo più semplice per usare un convertitore AD è il cosiddetto free running mode: consiste nel collegare direttamente l'uscita di fine conversione (EOC) con l'ingresso di inizio conversione (SOC) del convertitore. In questo modo al termine di ogni conversione ne viene avviata una nuova automaticamente, senza nessun intervento dall'esterno e il periodo di campionamento coincide esattamente col tempo impiegato dal convertitore per effettuare una conversione. Si consideri, a titolo di esempio, lo schema seguente, basato sul convertitore AD0804. Nello schema sono stati indicati solo i pin fondamentali per la comprensione del meccanismo di free running.

Si tratta di un convertitore a 8 bit, con uscite DB0, DB1,... DB7. ll segnale analogico di ingresso viene applicato in modo differenziale (senza riferimento a massa) fra i piedini Vin(+) e Vin(-).

Gli ingressi CS e RD, attivi bassi, sono collegati a massa in modo da attivare sempre l'integrato e abilitarne le uscite. L'ingresso di inizio conversione (denominato WR) è collegato direttamente con l'uscita di fine conversione (INTR), di modo che ogni conversione terminata ne avvi un'altra.

L'interruttore in ingresso serve per avviare la prima conversione (è necessario, altrimenti la sequenza di conversioni non inizierebbe mai).

Questa soluzione è semplice, ma presenta l'inconveniente di non poter modificare il periodo di campionamento. Inoltre il periodo di campionamento non viene temporizzato in modo preciso, poichè dipende essenzialmente dai ritardi interni all'ADC.

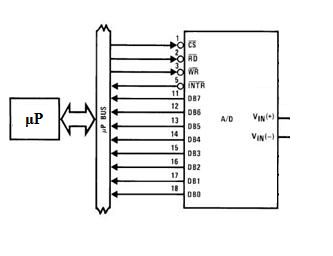

Una possibilità più evoluta consiste nell'interfacciare il convertitore AD con un microprocessore (µP), come mostrato in modo sintetico nella figura seguente:

In questo caso il µP si occupa di avviare ciascuna conversione e di leggere i valori presenti sui pin di uscita al termine di ogni conversione. Il periodo di campionamento viene in questo caso gestito dal µP stesso (temporizzazione software) oppure tramite hardware esterno (temporizzazione hardware).

Per temporizzazione software si intende l’esecuzione da parte del µP, all’inizio di ogni ciclo di regolazione, di un ciclo di ritardo di durata pari al periodo di campionamento. Questo tipo di temporizzazione è poco costosa, in quanto non richiede hardware aggiuntivo, ma presenta lo svantaggio di essere piuttosto imprecisa, soprattutto per periodi di campionamento molto lunghi. Inoltre durante il ciclo di ritardo il µP risulta impegnato inutilmente e non può essere usato per altri scopi.

La soluzione alternativa è costituita dalla cosiddetta temporizzazione hardware. In questo caso è necessario usare un timer esterno, cioè un dispositivo in grado di inviare al µP un segnale di interruzione (interrupt) allo scadere di ogni periodo di campionamento. Ogni volta che il µP riceve un segnale di interrupt dal timer, esso esegue una opportuna routine di servizio dell’interrupt, all’interno della quale viene acquisito un campione digitale.

Dal punto di vista del microprocessore il convertitore ADC è una periferica di input alla quale sono associate diverse porte per la lettura del dato convertito e per la gestione dei segnali di sincronismo (per una trattazione più generale dell'interfacciamento fra un µP e una periferica vedere l'apposito capitolo).

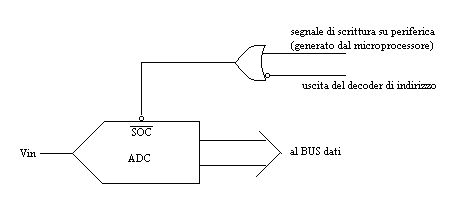

Allo scadere di ogni periodo di campionamento, il µP avvia la conversione inviando all’ADC un segnale impulsivo di start of conversion (SOC), che rappresenta il segnale detto in generale di strobe per l'interfacciamento fra µP e periferica. Ciò avviene eseguendo sul microprocessore una istruzione di invio dati a periferica (OUT) all'indirizzo del convertitore (il valore inviato con tale istruzione non ha nessuna importanza, dal momento che l’istruzione serve solo per attivare l’indirizzo dell’ADC). Lo schema di riferimento è mostrato in figura:

Nello schema in figura il segnale di start of conversion è attivo a livello basso. Per avviare la conversione, il microprocessore genera un segnale di scrittura su periferica (attivo anch'esso a livello basso); supponiamo invece che il decoder di indirizzo produca un segnale a livello alto, il quale viene inviato all’ADC. La porta OR pertanto produce un impulso di SOC a livello basso quando il µP effettua un’operazione di scrittura all’indirizzo del convertitore.

Una volta avviata la conversione, l’ADC segnala la fine della conversione, portando a livello alto una opportuna linea di uscita detta di end of conversion (EOC). La lettura del dato convertito non può avvenire dunque immediatamente dopo l’impulso di SOC, ma occorre prima attendere che l’ADC abbia completato la conversione.

Il modo più semplice per risolvere il problema consiste nel non testare il valore della linea di end of conversion. In pratica basta far eseguire al µP un ciclo di ritardo di durata opportuna fra l’avvio della conversione e la lettura del dato convertito. Lo svantaggio è che, per assicurare una corretta conversione in tutti i casi, occorre sovradimensionare la durata del ciclo di ritardo ed in tale modo la gestione del tempo non viene ottimizzata.

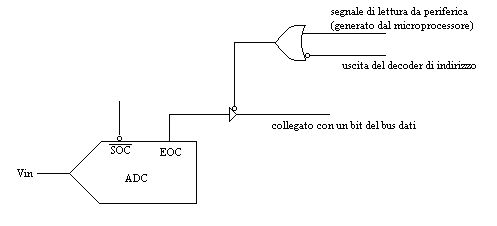

Un’altra possibilità consiste nell’interrogare ciclicamente in polling la linea EOC del convertitore (che in questo caso rappresenta il segnale detto di busy dell'handshaking bidirezionale col µP). L’interrogazione ciclica avviene eseguendo sul microprocessore una istruzione di lettura da periferica (IN) all’indirizzo assegnato alla linea EOC. Lo schema di riferimento è mostrato in figura:

L’alternativa più complicata per la gestione dell’EOC (e anche quella che ottimizza la gestione dei tempi) consiste nel generare un segnale di interrupt al µP ogni volta che è terminata una acquisizione. La routine di servizio dell'interrupt si occupa quindi di leggere il valore digitale convertito. Su alcuni ADC la gestione ad interrupt dell’end of conversion è suggerita dal nome stesso del segnale usato per segnalare la fine della conversione (INTR). In pratica basta collegare direttamente l’uscita INTR dell’ADC con l’ingresso di interrupt del µP (se non vi sono altri segnali di interrupt da gestire).

Sito realizzato in base al template offerto da

http://www.graphixmania.it